Products

Products

-

ESL Synthesis

-

Power Optimization

-

Functional Verification

- SLEC System •

- SLEC System-HLS •

- SLEC RTL •

- SLEC Pro •

-

White Papers

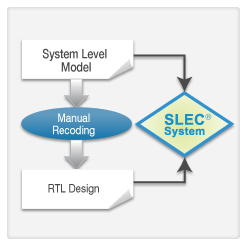

Benefits of SLEC System

- Leverages system-level models to verify RTL designs

- Keeps hardware intent consistent during system-level model refinement

- Verifies RTL blocks without waiting for the entire assembled design

- Replaces time consuming simulation regressions with fast results

- Isolates bugs quickly with short, concise debug waveforms

SLEC System verifies RTL designs and system-level models without testbenches or assertions.

Based on Calypto's patented Sequential Analysis Technology, SLEC System formally verifies equivalence of system-level models and RTL designs.

SLEC System finds design errors that other tools miss by formally comparing the functionality of an Electronic System Level (ESL) model written in C/C++/SystemC with its corresponding RTL design or system-level model for all possible input sequences. Unlike combinational equivalence checkers, SLEC System does not require one to one mapping of registers. The quality of verification SLEC System performs in minutes is equal to months of running simulation.

SLEC System either confirms that no functional errors exist or generates short, concise waveforms that pinpoint design bugs. These waveforms are written in standard VCD and FSDB formats that can be analyzed in the user’s native debugging environment.

SLEC System is part of Calypto’s SLEC family of proven sequential equivalence checking products. SLEC System includes all the capabilities of SLEC RTL and SLEC Pro.

Enabling ESL™

Datasheet

White Papers

Leveraging System Models for RTL Functional Verification using SLEC

Navigating the System to RTL Continuum

Verification Without Testbenches