Products

Products

-

ESL Synthesis

-

Power Optimization

-

Functional Verification

-

Benefits of Catapult C Synthesis

Dramatically shortens the design cycle

- Correct-by-construction designs

- Error-free RTL generation

- Zero iterations at the RTL

Immediate and measurable benefits

- Fastest path to verified RTL

- More gates produced per engineer

- Positive ROI on first design

Tested, proven, adopted worldwide

- #1 market share for past three years

- Hundreds of users and tape-outs

- Certified in TSMC Reference Flow 11

Reduce the Time to Verified RTL

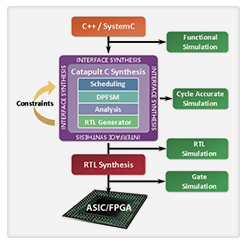

Traditional hardware design methods that require hand-written RTL development and debugging are too time-consuming and error prone for today’s complex designs. Catapult C Synthesis empowers designers to use industry standard ANSI C++ and SystemC to describe functional intent and move up to a more productive abstraction level. From these high-level descriptions, Catapult C Synthesis generates production quality RTL.

- Synthesizes ANSI C++ and SystemC to production quality RTL

- Targets algorithms, control-logic and interfaces for full-chip synthesis

- Dramatically shortens the path to verified RTL

Catapult gains SystemC, Low Power Support

SystemC Support

Calypto rolls-out SystemC synthesis, expands Catapult C Synthesis full-chip synthesis capabilities with the efficient handling of complex bus interfaces, SoC interconnects and TLM2.0-based ESL flows.

- Synthesizes SystemC input sources

- Supports cycle-accurate coding style for fine-grain control over design results

- Supports transaction-level modeling and ESL flows

- Supports complex buses and SoC interconnects

- Reads in legacy synthesizable SystemC IP descriptions

- Integrates with Mentor Graphics’ Vista platform

TSMC-Qualified

Catapult C Synthesis is now included in the TSMC Reference Flow 11.

- TSMC-qualified 40nm and 65nm low power process synthesis libraries for Catapult C Synthesis

- Integration of TSMC’s Memory Compiler in Catapult C Synthesis

Low Power Support

With its new built-in low power optimizations, Catapult C Synthesis automates prevailing low-power design technique and delivers unrivaled power reduction.

- Fully automated multi-level clock-gating providing near perfect clock gating

- Dynamic power management interfaces

- Reduces power consumption by an average 40%

Control-Logic Support

Catapult C added support for control-logic synthesis. It is the first unified solution that lets designers model, verify, and synthesize complex mixes of control and algorithmic units from a single ANSI C++ source.

- Supports synchronous reactive systems from pure C++

- Dedicated QoR optimizations for optimal control logic timing and area

- Enables mixing data-driven algorithmic blocks with clock-driven control units

Hitachi, Ltd. Leverages Catapult C Synthesis

“During the evaluation, we had a tricky corner-case bug that required 20k patterns of simulation data to trigger. While running those patterns took only an hour in the C simulation, and it would have...

View the Success Story

STMicroelectronics Utilizes Catapult C Synthesis

"With the Catapult C Synthesis flow, RTL debug literally disappears. The C model is validated in its environment, and from there correct-by-construction RTL is created. This reduces the verification...

View the Success Story

Ericsson Evaluates Catapult C Synthesis

Catapult C Synthesis reduces the Ericsson mobile platform team’s gate count by 30% and eliminates RTL design bottleneck.

Alcatel Space Adopts Catapult C Synthesis

Catapult C Synthesis helps the Alcatel Space division produce smaller and faster ASIC designs in far less time.

Products

Products